Serveis integrals de fabricació electrònica, us ajuden a aconseguir fàcilment els vostres productes electrònics de PCB i PCBA

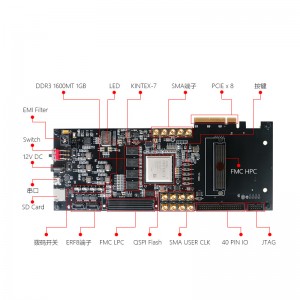

FPGA Xilinx K7 Kintex7 Comunicació per fibra òptica PCIe

- DDR3 SDRAM: 16 GB de DDR3 de 64 bits, velocitat de dades de 1600 Mbps

- Memòria flash QSPI: una peça de memòria flash QSPIP de 128 Mbit, que es pot utilitzar per a fitxers de configuració de FPGA i emmagatzematge de dades d'usuari.

- Interfície PCLEX8: La interfície PCLEX8 estàndard s'utilitza per comunicar-se amb la comunicació PCIE de la placa base de l'ordinador. Admet l'estàndard PCI Express 2.0. La velocitat de comunicació d'un sol canal pot arribar als 5 Gbps.

- Port sèrie USB UART: un port sèrie, connectat al PC mitjançant el cable miniUSB per realitzar comunicació sèrie

- Targeta Micro SD: seient de targeta Microsd completament, podeu connectar la targeta Microsd estàndard

- Sensor de temperatura: un xip de sensor de temperatura LM75, que pot controlar la temperatura ambiental al voltant de la placa de desenvolupament

- Port d'extensió FMC: un FMC HPC i un FMCLPC, que poden ser compatibles amb diverses targetes d'expansió estàndard

- Terminal de connexió d'alta velocitat ERF8: 2 ports ERF8, que admeten la transmissió de senyal d'ultra alta velocitat. Extensió de 40 pins: reservada una interfície d'E/S d'extensió general amb 2,54 mm i 40 pins, O efectiu té 17 parells, suporta 3,3 V.

- La connexió perifèrica del nivell i el nivell de 5V poden connectar els perifèrics perifèrics de diferents interfícies 1O d'ús general

- Terminal SMA; 13 capçals SMA xapats en or d'alta qualitat, que són convenients per als usuaris per cooperar amb targetes d'expansió AD/DA FMC d'alta velocitat per a la recollida i el processament de senyals

- Gestió del rellotge: Font multirellotge. Inclou la font de rellotge diferencial del sistema de 200 MHz SIT9102

- Cristal diferencial oscil·lant: cristall de 50 MHz i xip de gestió de rellotge programable SI5338P: també equipat amb

- EMCCLK de 66 MHz. S'adapta amb precisió a diferents freqüències de rellotge d'ús

- Port JTAG: port JTAG estàndard de 2,54 mm i 10 puntades, per a la descàrrega i depuració de programes FPGA

- Xip de monitorització de voltatge de subreinici: una peça de xip de monitorització de voltatge ADM706R i el botó amb el botó proporciona un senyal de reinici global per al sistema

- LED: 11 llums LED, indiquen l'alimentació de la placa base, senyal config_done, FMC

- Senyal indicador d'alimentació i 4 LED d'usuari

- Tecla i interruptor: 6 tecles i 4 interruptors són botons de reinici FPGA,

- El botó del programa B i 4 tecles d'usuari estan compostos. 4 interruptors de doble ganivet simple

Escriu el teu missatge aquí i envia'ns-el

Categories de productes

-

Telèfon

-

Correu electrònic

-

WhatsApp

-

Skype

-

Skype

-

Skype